W5300 회로 설계시 주의 사항

wiznet.co.kr 에서 8채널 소켓, 8/16bit 128Kbyte로 업그레이드된 Hardware TCP/IP 칩셋이 새롭게 출시 되었다.

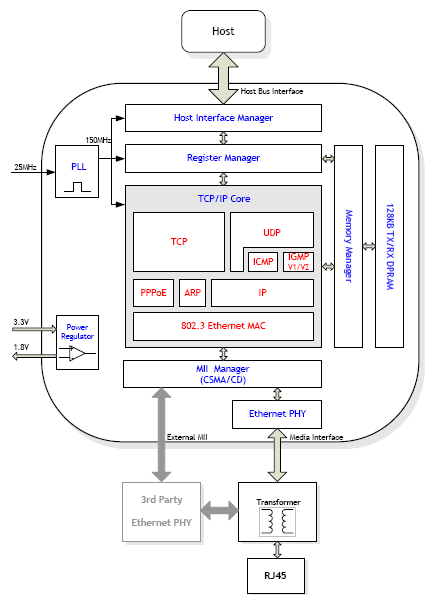

W5300은 위즈네트의 Hardware TCP/IP 기술을 이용한 임베디드 시스템을 위한 인터넷 솔루션 중 멀티미디어 서비스에 적합한 고성능에 목적을 둔 제품이다. 기존의 위즈네트 칩에 비해서 메모리 및 데이터 처리 부분을 개선하여 성능을 향상시켰으며, 최근 각광을 받고 있는 IPTV, IP-STB등의 대용량 멀티미디어 데이터 전송에 대응할 수 있도록 개발된 제품이다. W5300 하나의 칩으로 TCP/IP 프로토콜 처리 및 10/100 Ethernet PHY와 MAC을 구현하여 개발하고자 하는 Application에 Internet Connectivity를 손쉽게 구현할 수 있도록 지원한다.

위즈네트에서는 TCP, UDP, IPv4, ICMP, IGMP, ARP, PPPoE 등의 통신 프로토콜을 Full hardware logic으로 개발하여 여러 제품에서 사용하고 있다. W5300에서는 보다 고성능의 데이터 통신을 제공하기 위해서 data communication memory를 128Kbyte로 확장하고, 16bit bus interface를 지원한다. 이에 사용자는 W5300의 하드웨어로 처리되는 8개의 독립적인 고속의 하드웨어 SOCKET을 사용할 수 있다.

W5300의 Host Interface 방식은 SRAM 메모리등과 같은 System bus interface를 제공하며 Direct address access 방식과 Indirect address access방식을 지원하여 메모리를 사용하듯 쉽게 사용할 수 있도록 한다. 또한 W5300의 Data communication memory는 각 SOCKET별로 존재하는 송신 FIFO Register와 수신 FIFO Register를 통해서 간단히 Access 할 수 있도록 하여 보다 쉽고 간단히 W5300을 사용할 수 있도록 하여 네트워크를 처음 접하는 엔지니어도 쉽게 Internet connectivity를 구현할 수 있도록 지원한다.

주요 핀 기능

BIT16EN

16/8 BIT DATA BUS SELECT

High : 16 bit data bus, Low : 8 bit data bus Data bus width를 결정한다.

이 Signal은 Reset 시 내부적으로 Mode register(MR)의 15번째 Bit(?BW?)로 Latch되며, Reset 이후의 Signal 변화는 무시된다. 즉 Reset 이후 Data bus width를 변경할 수 없다. 8bit data bus를 사용할 경우 반드시 Ground 처리한다.

ADDR9~0

ADDRESS System address bus. W5300의 Host interface mode와 Data bus width에 따라 선택적으로 사용될 수 있다.

16 Bit Data bus를 사용할 경우 ADDR0은 내부적으로 무시된다.

BRDY[3:0]

Buffer Ready Indicator 각 PIN들은 사용자에 의해 SOCKET Number, Memory Type, Buffer Depth등을 설정되고, 설정된 SOCKET의 Memory가 Buffer Depth보다 크거나 같을 경우 High나 Low로 Signal된다.

TEST_MODE[3:0]

W5300 MODE SELECT

일반적인 경우 내부 PHY를 사용하므로 "0000"로 설정하면 된다.

OP_MODE[2:0]

Internal PHY Operation Control Mode

이것도 "000" Auto 모드로 설정 하면 된다.

레퍼런스 회로도

내부 PHY 사용:

Direct 16 Bit Data Bus Width

16bit data bus width를 사용할 경우, ADDR[9:1]만 사용되며, ADDR0은 Float나 Ground 처리한다. „BIT16EN‟은 내부적으로 Pull-up 처리되어 있어 Float 시켜도 무방하다.

Direct 8 Bit Data Bus Width

8bit data bus width를 사용할 경우, ADDR[9:0] 모두 사용되며, „BIT16EN‟은 반드시 Logical LOW(Ground) 처리한다. 사용하지 않는 DATA[15:8]은 모두 Float 시킨다.

8bit data bus width를 사용할 경우, ADDR[9:0] 모두 사용되며, „BIT16EN‟은 반드시 Logical LOW(Ground) 처리한다. 사용하지 않는 DATA[15:8]은 모두 Float 시킨다.

Indirect 16 Bit Data Bus Width

16bit data bus width를 사용할 경우, ADDR[2:1]만 사용되며, ADDR[9:3]과 ADDR0은 Float나Ground 처리한다. „BIT16EN‟은 내부적으로 Pull-up 처리되어 있어 Float 시켜도 무방하다.

16bit data bus width를 사용할 경우, ADDR[2:1]만 사용되며, ADDR[9:3]과 ADDR0은 Float나Ground 처리한다. „BIT16EN‟은 내부적으로 Pull-up 처리되어 있어 Float 시켜도 무방하다.

8bit data bus width를 사용할 경우, ADDR[2:0]만 사용되며, ADDR[9:3]은 Float나 Ground 처리한다. „BIT16EN‟은 반드시 Ground 처리한다. 사용하지 않는 DATA[15:8]은 모두 Float 시킨다.

전압 전류 특성

3.3V로 구동되며 5V tolerance를 가진다.

반응형

invalid-file

invalid-file invalid-file

invalid-file