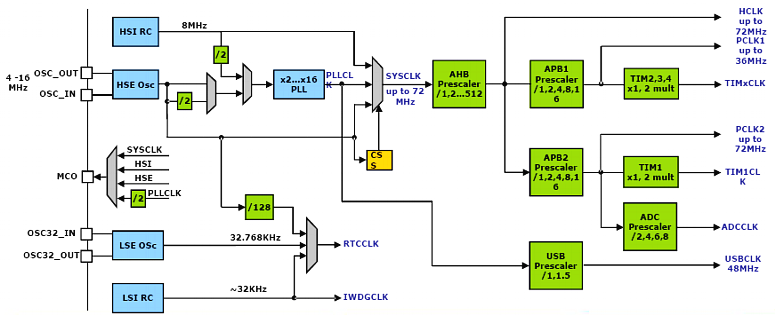

[STM32] CLOCK

클럭 소스는 내부 8Mhz의 RC오실레이터나 외부 4~16Mhz크리스탈, OSC32 32Khz로 공급된다.

클럭 소스는 내부 8Mhz의 RC오실레이터나 외부 4~16Mhz크리스탈, OSC32 32Khz로 공급된다.

SYSCLK(System Clock) sources

HSI, HSE, PLL에서 공급되며 AHB, APB1/2, ADC and TIM clocks 으로 사용 한다.

HSI, HSE, PLL에서 공급되며 AHB, APB1/2, ADC and TIM clocks 으로 사용 한다.

USBCLK(USB Clock)

내부 PLL으로 부터 생성해서 USB 엔진에 공급된다.

내부 PLL으로 부터 생성해서 USB 엔진에 공급된다.

RTCCLK(RTC Clock)

LSE, LSI, HSE/128 으로 공급된다.

LSE, LSI, HSE/128 으로 공급된다.

CSS(Clock Security System)

HSE실패를 대비한 백업클럭

HCLK

코어 클럭으로 72Mhz까지 가능

STM32 전체 Clock 구조

BusMatrix와 Harvard architecture로 SRAM, Flash, Peripherals, DMA를 동시에 접근가능해 병목현상이 상당히 줄어 속도를 향상 시겼다고 함.

BusMatrix와 Harvard architecture로 SRAM, Flash, Peripherals, DMA를 동시에 접근가능해 병목현상이 상당히 줄어 속도를 향상 시겼다고 함.

클럭설정을 위해 먼저 내부클럭(HSI), 외부클럭 (HSE)를 사용할것인지를 설정한다.

ST에서 제공하는 RCC관련 stm32f10x_rcc.c 파일에서 RCC_HSEConfig()함수를 사용해서 RCC_HSE_ON, RCC_HSE_Bypass를 결정할 수 있다.

RCC_PLLConfig함수에서 PLL설정 가능하다.

/* PLLCLK = 8MHz * 9 = 72 MHz */

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);

HCLK, PCLK1 , PCLK2 등 클럭 설정을 RCC_Configuration()함수로 만들어 관리하면 편하게 사용할 수 있다.

void RCC_Configuration(void)

{

/* RCC system reset(for debug purpose) */

RCC_DeInit();

{

/* RCC system reset(for debug purpose) */

RCC_DeInit();

/* Enable HSE */

RCC_HSEConfig(RCC_HSE_ON);

RCC_HSEConfig(RCC_HSE_ON);

/* Wait till HSE is ready */

HSEStartUpStatus = RCC_WaitForHSEStartUp();

HSEStartUpStatus = RCC_WaitForHSEStartUp();

if(HSEStartUpStatus == SUCCESS)

{

/* Enable Prefetch Buffer */

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

{

/* Enable Prefetch Buffer */

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);

/* Flash 2 wait state */

FLASH_SetLatency(FLASH_Latency_2);

/* HCLK = SYSCLK */

RCC_HCLKConfig(RCC_SYSCLK_Div1);

/* PCLK2 = HCLK */

RCC_PCLK2Config(RCC_HCLK_Div1);

FLASH_SetLatency(FLASH_Latency_2);

/* HCLK = SYSCLK */

RCC_HCLKConfig(RCC_SYSCLK_Div1);

/* PCLK2 = HCLK */

RCC_PCLK2Config(RCC_HCLK_Div1);

/* PCLK1 = HCLK/2 */

RCC_PCLK1Config(RCC_HCLK_Div2); //run 72Mhz @Div2

/* PLLCLK = 8MHz * 9 = 72 MHz */

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);

/* Enable PLL */

RCC_PLLCmd(ENABLE);

/* Wait till PLL is ready */

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET)

{

}

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET)

{

}

/* Select PLL as system clock source */

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK);

/* Wait till PLL is used as system clock source */

while(RCC_GetSYSCLKSource() != 0x08)

{

}

}

}

- PCLK1 은 Timer 등 많은 페리가 연결되어 있는데 Div2일때 최대 72Mhz 로 동작한다.

while(RCC_GetSYSCLKSource() != 0x08)

{

}

}

}

- PCLK1 은 Timer 등 많은 페리가 연결되어 있는데 Div2일때 최대 72Mhz 로 동작한다.

반응형