Future Technology Devices International Ltd.

# UNCULUM BINDING USB TECHNOLOGIES

# Vinculum VNC1L Embedded USB Host Controller I.C.

The Vinculum VNC1L is the first of FTDI's Vinculum family of Embedded USB host controller integrated circuit devices. Not only is it able to handle the USB Host Interface, and data transfer functions but owing to the inbuilt MCU and embedded Flash memory, Vinculum can encapsulate the USB device classes as well. When interfacing to mass storage devices such as USB Flash drives, Vinculum also transparently handles the FAT File structure communicating via UART, SPI or parallel FIFO interfaces via a simple to implement command set. Vinculum provides a new cost effective solution for providing USB Host capability into products that previously did not have the hardware resources available.

The VNC1L is available in Pb-free (RoHS compliant) compact 48-Lead LQFP package.

http://www.vinculum.com

#### 1.1 Hardware Features

- Single chip embedded USB host / slave controller

I.C. device

- Entire USB protocol handled on the chip

- 8 / 32 bit V-MCU Core

- Twin DMA controllers for hardware acceleration

- Integrated 12 MHz to 48 MHz clock multiplier

- Integrated power-on-reset circuit with optional RESET# input pin

- 64k byte embedded Flash ROM program memory

- 4k byte internal data SRAM

- Standard USB firmware library supplied by FTDI

- Program or update firmware via USB Flash disk or UART interface

- Firmware easily upgradable in the field

- PROG# firmware programming control pin

- Two independent USB 2.0 Low speed / Full speed USB Host / Slave ports with integrated pull-up and pull-down resistors

- Four fully configurable data I/O and control Buses

- UART interface mode for data I/O, firmware programming, and command monitor interface

- FIFO interface mode with 8 bit bi-directional data bus and simple 4 wire handshake for data I/O and command monitor interface

- SPI slave interface mode for data I/O and command monitor interface

- Up to 28 GPIO interface pins for data I/O and command monitor interface

- Interface to MCU / PLD / FPGA via UART, FIFO, or SPI interface

- Legacy PS/2 keyboard and mouse interfaces

- Multi-processor configuration capable

- Support for USB suspend and resume

- Support for bus powered, self powered, and highpower bus powered USB device configurations

2) (a particular with 5) (a pfe inputs)

- 3.3V operation with 5V safe inputs

- Low operating and USB suspend current (25mA running / 2mA stnadby)

- Fully compliant with USB 2.0 specification USB full speed (12 Mbps) and low speed (1.5 Mbps) USB host and slave device compatible

- 0°C to 70°C operating temperature range

- Full driver support for target / slave applications

- Available in compact Pb-free and green 48 Pin LQFP package (RoHS compliant)

- Full range of reference designs and evaluation kits available

#### **1.2 Standard Firmware**

• USB slave device and USB Flash disk interface with selectable UART / FIFO / SPI interface or USB slave device as the command monitor port (VDIF firmware)

•

- FTDI USB slave device and USB Flash disk interface with selectable UART / FIFO / SPI interface as the command monitor port (VDAP firmware)

- USB Flash disk to USB Flash disk with GPIO command monitor interface (VDFC firmware)

- FTDI USB slave device and USB Flash disk interface with selectable UART / FIFO / SPI interface as the command monitor port with audio playback command extensions (VMSC firmware)

#### **1.3 Typical Applications**

- Add USB host capability to embedded products

- Interface USB Flash drive to MCU / PLD / FPGA

- USB Flash drive to USB Flash drive file transfer interface

- Digital camera to USB Flash drive or other USB slave device interface

- PDA to USB Flash driver or other USB slave device interface

- MP3 Player to USB Flash drive or other USB slave device interface

- USB MP3 Player to USB MP3 Player

- Mobile phone to USB Flash drive or other USB slave device interface

- GPS to mobile phone interface

- Instrumentation USB Flash drive or other USB slave device interfacing

- Datalogger USB Flash drive or other USB slave device interface

- Set Top Box USB device interface

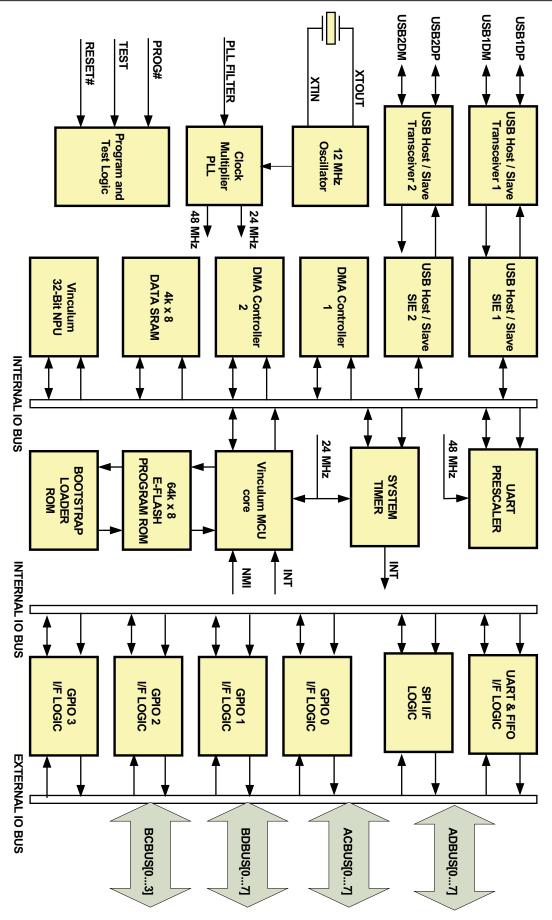

### 2. Block Diagram

#### 2.1 Simplified Block Diagram

#### Figure 1 - Simplified Block Diagram

#### **2.2 Functional Block Descriptions**

**USB Host / Slave Transceivers 1 and 2 -** The two USB transceiver cells provide the USB host / slave physical USB 1.1 / USB 2.0 full-speed device interface. On each the output drivers provide 3.3V level slew rate control signalling, whilst a differential receiver and two single ended receivers provide USB data in, SEO and USB Reset condition detection. These cells also incorporate internal USB pull-up or pull down resistors as required for host or slave mode.

**USB Host / Slave Serial Interface Engine ( SIE )** - These blocks handle the parallel to serial and serial to parallel conversion of the USB Physical layer including bit suffing / unstuffing, CRC generation / checking, USB frame generation and error checking.

**12 MHz Oscillator -** The 12MHz Oscillator cell generates a 12MHz reference clock input to the Clock Multiplier PLL from an external 12MHz crystal.

**Clock Multiplier PLL -** The Clock Multiplier PLL takes the 12MHz input from the Oscillator Cell and generates 24MHz and 48MHz reference clock signals, which is used by the USB SIE Blocks, the MCU core, System Timer and UART Prescaler blocks.

**Program and Test Logic -** this block provides a means of programming the onboard E-Flash memory. When PROG# is pulled low and the device is reset, the onboard E-Flash memory is bypassed by an internal hard coded BootStrap Loader ROM which contains code to allow the E-Flash memory to be programmed via commands to the UART interface. FTDI provides a software utility which allows the VNC1L to be programmed using this method. The TEST pin is used in manufacturing to enhance the testability of the various internal blocks and should be tied to GND.

**DMA Controller 1 and 2 -** The twin DMA controllers in the VNC1L greatly enhance performance by allowing data from the two USB SIE controllers, UART, FIFO and SPI to be transferred between each other via the data SRAM with minimal MCU intervention.

**Data SRAM -** This 4k x 8bit block acts as the data (variable) memory for the Vinculum MCU, though it can also be accessed transparently to the MCU by the twin DMA controllers.

**NPU (Numeric CoProcessor ) -** Most Vinclum MCU operations are 8-bit, however there are some scenarios such as transversing disk FAT tables which involve extensive 32 bit arithmetic. In order to speed up these operations, the MCU has a dedicated 32 bit co-processor block.

**UART Prescaler -** this block provides the master transmit / receive clock for the UART block. By varying the prescalar value, the baud rate of the UART can be adjusted over a range of 300 baud to 1M baud.

**SYSTEM TIMER -** The system timer provides a regular interrupt to the Vinculum MCU, typically at 1mS intervals. This is used by the MCU to provide timeouts and other timing functions.

**VINCULUM MCU CORE -** The "heart" of the VNC1L is the VMCU core based on FTDI's proprietary 8-bit embedded MCU (EMCU) architectiure. VMCU has a Harvard architecture i.e. separate code and data space and supports 64k byes of program code, 64k byes of (paged) data space and 256 bytes of IO space. It uses "enhanced CISC" technology - typically VNCU instructions would replace several lines of code in conventional CISC or RISC processors giving RISC like performance in a CISC architecture with the advantage over both of excellent code compression in the program ROM space.

**E-FLASH Program ROM -** The VNCL1L has 64k bytes of embedded Flash (E-Flash) memory. No special programming voltages are necessary for programming the onboard E-FLASH as these are provided internally on-chip. Common methods of programming the E-FLASH (both under control of the VMCU) are via the UART by pulling the PROG# pin low and resetting the device OR by using the programming via a USB FLASH drive feature provided in many of the VNC1L firmware packages.

**BOOTSTRAP LOADER ROM -** This is a small block of hard encoded ROM (512 x 8 bits) which bypasses the main e\_FLASH memory when PROG# is pulled low. This provides a means of programming the entire E-Flash memory via the UART interface.

**UART and FIFO Logic -** These provide optional serial and parallel interfaces to the VNC1L equivalent to the interfaces on FTDI's FT232 and FT245 USB UART and FIFO products.

**GPIO Blocks** - general purpose IO pins. See the tables below to determine which are available for any specific configuration.

2. Device Pin Out and Signal Descriptions

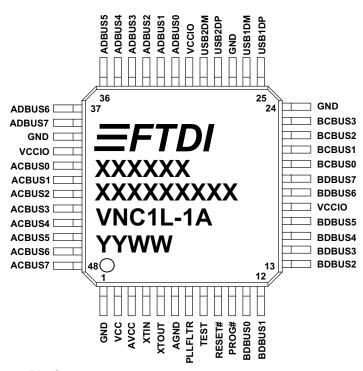

#### 2.1 48 Lead LQFP Pin Out

Figure 2 - 48 pin LQFP Package Pin Out

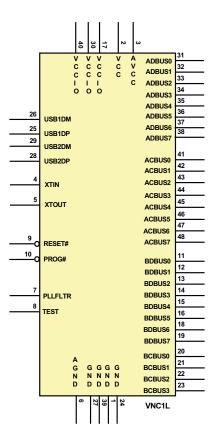

Figure 3 - VNC1L Pin Out - Schematic

#### Table 1 - Pin Out Description

| Pin No.                | Name                                                                                                       | Туре    | Description                                                                                                              |                                                                                                                                                                                                                               |                            |                        |              |  |  |

|------------------------|------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------|--------------|--|--|

| USB Interface Group    |                                                                                                            |         |                                                                                                                          |                                                                                                                                                                                                                               |                            |                        |              |  |  |

| 25                     | 25 USB1DP I/O USB host / slave port 1 - USB Data Signal Plus with integrated pull up / pull down resistor. |         |                                                                                                                          |                                                                                                                                                                                                                               |                            |                        |              |  |  |

| 26                     | USB1DM                                                                                                     | I/O     | USB host / slave port 1 - USB Data Signal Minus w                                                                        | 3 host / slave port 1 - USB Data Signal Minus with integrated pull up / pull down resistor.                                                                                                                                   |                            |                        |              |  |  |

| 28                     | USB2DP                                                                                                     | I/O     | USB host / slave port 2 - USB Data Signal Plus wit                                                                       | h integrated pu                                                                                                                                                                                                               | ll up / pull down          | resistor.              |              |  |  |

| 29                     | USB2DM                                                                                                     | I/O     | USB host / slave port 2 - USB Data Signal Minus w                                                                        | ith integrated p                                                                                                                                                                                                              | ull up / pull dow          | n resistor.            |              |  |  |

| Power and Ground Group |                                                                                                            |         |                                                                                                                          |                                                                                                                                                                                                                               |                            |                        |              |  |  |

| 1, 24, 27, 39          | GND                                                                                                        | PWR     | Device ground supply pins                                                                                                |                                                                                                                                                                                                                               |                            |                        |              |  |  |

| 2                      | VCC                                                                                                        | PWR     | 3.3V supply to the device core.                                                                                          |                                                                                                                                                                                                                               |                            |                        |              |  |  |

| 3                      | AVCC                                                                                                       | PWR     | +3.3V supply to the internal clock multiplier. This pi                                                                   | n requires a 10                                                                                                                                                                                                               | 0 nF decoupling            | capacitor.             |              |  |  |

| 6                      | AGND                                                                                                       | PWR     | Device analog ground supply for internal clock mult                                                                      | e analog ground supply for internal clock multiplier                                                                                                                                                                          |                            |                        |              |  |  |

| 17, 30, 40             | VCCIO                                                                                                      | PWR     | +3.3V supply to the ADBUS, ACBUS, BDBUS and                                                                              | BCBUS Interfa                                                                                                                                                                                                                 | ce pins (1116,             | 1823, 313              | 8, 4148).    |  |  |

| Miscellane             | ous Sign                                                                                                   | al Grou | p                                                                                                                        |                                                                                                                                                                                                                               |                            |                        |              |  |  |

| 4                      |                                                                                                            |         |                                                                                                                          |                                                                                                                                                                                                                               |                            |                        | threshold of |  |  |

| 5                      | XTOUT                                                                                                      | Output  | Output from 12MHz Oscillator Cell. Connect 12 MH<br>capacitors to GND. XTOUT stops oscillating during<br>external logic. |                                                                                                                                                                                                                               |                            |                        |              |  |  |

| 7                      | PLLFLTR                                                                                                    | Input   | External PLL filter circuit input. RC filter circuit mus                                                                 | t be fitted on th                                                                                                                                                                                                             | is pin.                    |                        |              |  |  |

| 8                      | TEST                                                                                                       | Input   | Puts the device into I.C. test mode. Must be tied to                                                                     | GND for norma                                                                                                                                                                                                                 | al operation.              |                        |              |  |  |

| 9                      | RESET#                                                                                                     | Input   |                                                                                                                          | Can be used by an external device to reset the VNC1L. This pin can be used in combination with PROG# and the UART interface to program firmware into the VNC1L. If not required pull up to VCC via a 10 k $\Omega$ resistor * |                            |                        |              |  |  |

| 10                     | PROG#                                                                                                      | Input   | This pin is used in combination with the RESET# p VNC1L.*                                                                | in and the UAR                                                                                                                                                                                                                | T interface to p           | rogram firmwa          | re into the  |  |  |

| Data and C             | ontrol Bu                                                                                                  | ıs Sian |                                                                                                                          |                                                                                                                                                                                                                               |                            |                        |              |  |  |

|                        |                                                                                                            |         |                                                                                                                          | Interface Mod                                                                                                                                                                                                                 | de                         |                        |              |  |  |

|                        |                                                                                                            |         |                                                                                                                          | UART Inter-<br>face                                                                                                                                                                                                           | Parallel FIFO<br>Interface | SPI Slave<br>Interface | I/O Port     |  |  |

| 11                     | BDBUS0                                                                                                     | I/O     | 5V safe bidirectional data / control bus, BD bit 0                                                                       |                                                                                                                                                                                                                               |                            |                        | PortBD0      |  |  |

| 12                     | BDBUS1                                                                                                     | I/O     | 5V safe bidirectional data / control bus, BD bit 1                                                                       |                                                                                                                                                                                                                               |                            |                        | PortBD1      |  |  |

| 13                     | BDBUS2                                                                                                     | I/O     | 5V safe bidirectional data / control bus, BD bit 2                                                                       |                                                                                                                                                                                                                               |                            |                        | PortBD2      |  |  |

| 14                     | BDBUS3                                                                                                     | I/O     | 5V safe bidirectional data / control bus, BD bit 3                                                                       |                                                                                                                                                                                                                               |                            |                        | PortBD3      |  |  |

| 15                     | BDBUS4                                                                                                     | I/O     | 5V safe bidirectional data / control bus, BD bit 4                                                                       |                                                                                                                                                                                                                               |                            |                        | PortBD4      |  |  |

| 16                     | BDBUS5                                                                                                     | I/O     | 5V safe bidirectional data / control bus, BD bit 5                                                                       |                                                                                                                                                                                                                               |                            |                        | PortBD5      |  |  |

| 18                     | BDBUS6                                                                                                     | I/O     | 5V safe bidirectional data / control bus, BD bit 6                                                                       |                                                                                                                                                                                                                               |                            |                        | PortBD6      |  |  |

| 19                     | BDBUS7                                                                                                     | I/O     | 5V safe bidirectional data / control bus, BD bit 7                                                                       |                                                                                                                                                                                                                               |                            |                        | PortBD7      |  |  |

| 20                     | BCBUS0                                                                                                     | I/O     | 5V safe bidirectional data / control bus, BC bit 0                                                                       | PS2Clk1**                                                                                                                                                                                                                     | PS2Clk1**                  | PS2Clk1**              | PortBC0      |  |  |

| 21                     | BCBUS1                                                                                                     | I/O     | 5V safe bidirectional data / control bus, BC bit 1                                                                       | PS2Data1**                                                                                                                                                                                                                    | PS2Data1**                 | PS2Data1**             | PortBC1      |  |  |

| 22                     | BCBUS2                                                                                                     | I/O     | 5V safe bidirectional data / control bus, BC bit 2                                                                       | PS2Clk2**                                                                                                                                                                                                                     | PS2Clk2**                  | PS2Clk2**              | PortBC2      |  |  |

| 23                     | BCBUS3                                                                                                     | I/O     | 5V safe bidirectional data / control bus, BC bit 3                                                                       | PS2Data2**                                                                                                                                                                                                                    | PS2Data2**                 | PS2Data2**             | PortBC3      |  |  |

| 31                     | ADBUS0                                                                                                     | I/O     | 5V safe bidirectional data / control bus, AD bit 0                                                                       | TXD                                                                                                                                                                                                                           | D0                         | SCLK                   | PortAD0      |  |  |

| 32                     | ADBUS1                                                                                                     | I/O     | 5V safe bidirectional data / control bus, AD bit 1                                                                       | RXD                                                                                                                                                                                                                           | D1                         | SDI                    | PortAD1      |  |  |

| 33                     | ADBUS2                                                                                                     | I/O     | 5V safe bidirectional data / control bus, AD bit 2                                                                       | RTS#                                                                                                                                                                                                                          | D2                         | SDO                    | PortAD2      |  |  |

| 34                     | ADBUS3                                                                                                     | I/O     | 5V safe bidirectional data / control bus, AD bit 3                                                                       | CTS#                                                                                                                                                                                                                          | D3                         | CS                     | PortAD3      |  |  |

| 35                     | ADBUS4                                                                                                     | I/O     | 5V safe bidirectional data / control bus, AD bit 4                                                                       | DTR#                                                                                                                                                                                                                          | D4                         |                        | PortAD4      |  |  |

| 36                     | ADBUS5                                                                                                     | I/O     | 5V safe bidirectional data / control bus, AD bit 5                                                                       | DSR#                                                                                                                                                                                                                          | D5                         | ļ                      | PortAD5      |  |  |

| 37                     | ADBUS6                                                                                                     | I/O     | 5V safe bidirectional data / control bus, AD bit 6                                                                       | DCD#                                                                                                                                                                                                                          | D6                         | ļ                      | PortAD6      |  |  |

| 38                     | ADBUS7                                                                                                     | I/O     | 5V safe bidirectional data / control bus, AD bit 7                                                                       | RI#                                                                                                                                                                                                                           | D7                         |                        | PortAD7      |  |  |

| 41                     | ACBUS0                                                                                                     | I/O     | 5V safe bidirectional data / control bus, AC bit 0                                                                       | TXDEN#                                                                                                                                                                                                                        | RXF#                       |                        | PortAC0      |  |  |

#### Table 1 continued - Pin Out Description

| 42 | ACBUS1 | I/O | 5V safe bidirectional data / control bus, AC bit 1                                                                                                                                                                                                                                                                                   | TXE# | PortAC1 |

|----|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 43 | ACBUS2 | I/O | 5V safe bidirectional data / control bus, AC bit 2                                                                                                                                                                                                                                                                                   | RD#  | PortAC2 |

| 44 | ACBUS3 | I/O | 5V safe bidirectional data / control bus, AC bit 3                                                                                                                                                                                                                                                                                   | WR   | PortAC3 |

| 45 | ACBUS4 | I/O | 5V safe bidirectional data / control bus, AC bit 4                                                                                                                                                                                                                                                                                   |      | PortAC4 |

| 46 | ACBUS5 | I/O | 5V safe bidirectional data / control bus, AC bit 5                                                                                                                                                                                                                                                                                   |      | PortAC5 |

| 47 | ACBUS6 | I/O | 5V safe bidirectional data / control bus, AC bit 6                                                                                                                                                                                                                                                                                   |      | PortAC6 |

| 48 | ACBUS7 | Ι/Ο | 5V safe bidirectional data / control bus, AC bit 7.<br>To use a 12 MHz crystal with the VNC1L fit a 47 k $\Omega$ pull-down resistor. Alternatively, fitting a 47 k $\Omega$ pull-up resistor on this pin will switch off the internal clock multiplier, allowing the device to be fed with an external 48Mz clock signal into XTIN. |      | PortAC7 |

\* These pins are pulled to VCC via internal 200k $\Omega$  resistors.

\*\* PS/2 Ports can be available while UART, FIFO, or SPI interface is enabled.

#### 2.3 UART Interface Signal Descriptions

| Pin No. | Name  | Туре   | Description                                                                                                                                                          |

|---------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31      | TXD   | Output | Transmit asynchronous data output                                                                                                                                    |

| 32      | RXD   | Input  | Receive asynchronous data input                                                                                                                                      |

| 33      | RTS#  | Output | Request To Send Control Output / Handshake signal                                                                                                                    |

| 34      | CTS#  | Input  | Clear To Send Control Input / Handshake signal                                                                                                                       |

| 35      | DTR#  | Output | Data Terminal Ready Control Output / Handshake signal                                                                                                                |

| 36      | DSR#  | Input  | Data Set Ready Control Input / Handshake signal                                                                                                                      |

| 37      | DCD#  | Input  | Data Carrier Detect Control Input                                                                                                                                    |

| 38      | RI#   | Input  | Ring Indicator Control Input. When the Remote Wake up option is enabled in the EEPROM, taking RI# low can be used to resume the PC USB Host controller from suspend. |

| 41      | TXDEN | Output | Enable Transmit Data for RS485 designs                                                                                                                               |

Table 4 - Data and Control Bus Signal Mode Options - UART Interface

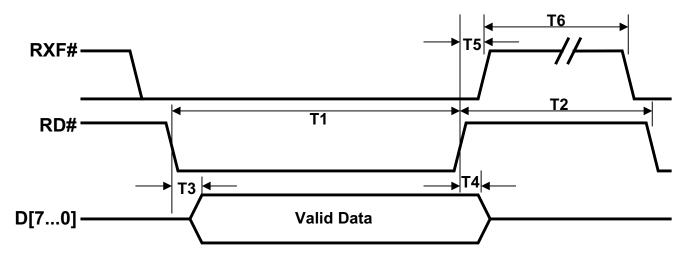

#### 2.4 Parallel FIFO Interface Signal Descriptions and Timing Diagrams

Table 5 - Data and Control Bus Signal Mode Options - Parallel FIFO Interface

| Pin No. | Name | Туре   | Description                                                                                                                                                          |

|---------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31      | D0   | I/O    | FIFO Data Bus Bit 0                                                                                                                                                  |

| 32      | D1   | I/O    | FIFO Data Bus Bit 1                                                                                                                                                  |

| 33      | D2   | I/O    | FIFO Data Bus Bit 2                                                                                                                                                  |

| 34      | D3   | I/O    | FIFO Data Bus Bit 3                                                                                                                                                  |

| 35      | D4   | I/O    | FIFO Data Bus Bit 4                                                                                                                                                  |

| 36      | D5   | I/O    | FIFO Data Bus Bit 5                                                                                                                                                  |

| 37      | D6   | I/O    | FIFO Data Bus Bit 6                                                                                                                                                  |

| 38      | D7   | I/O    | FIFO Data Bus Bit 7                                                                                                                                                  |

| 41      | RXF# | OUTPUT | When high, do not read data from the FIFO. When low, there is data available in the FIFO which can be read by strobing RD# low, then high again.                     |

| 42      | TXE# | OUTPUT | When high, do not write data into the FIFO. When low, data can be written into the FIFO by strobing WR high, then low.                                               |

| 43      | RD#  | INPUT  | Writes the data byte on the D0D7 pins into the transmit FIFO buffer when WR goes from high to low.                                                                   |

| 44      | WR   | INPUT  | Enables the current FIFO data byte on D0D7 when low. Fetched the next FIFO data byte (if avail-<br>able) from the receive FIFO buffer when RD# goes from high to low |

#### Table 6 - FIFO Read Cycle Timings

| Time | Description                            | Min     | Max | Unit |

|------|----------------------------------------|---------|-----|------|

| T1   | RD Active Pulse Width                  | 50      | -   | ns   |

| T2   | RD to RD Pre-Charge Time               | 50 + T6 | -   | ns   |

| Т3   | RD Active to Valid Data*               | 20      | 50  | ns   |

| T4   | Valid Data Hold Time from RD Inactive* | 0       | -   | ns   |

| T5   | RD Inactive to RXF#                    | 0       | 25  | ns   |

| Т6   | RXF Inactive After RD Cycle            | 80      | -   | ns   |

\* Load = 30pF

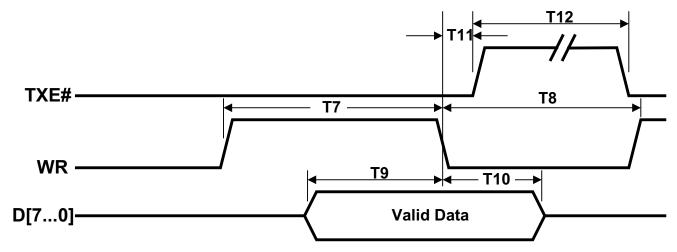

Figure 5 - FIFO Write Cycle

#### Table 7 - FIFO Write Cycle Timings

| Time | Description                        | Min | Max | Unit |

|------|------------------------------------|-----|-----|------|

| T7   | WR Active Pulse Width              | 50  | -   | ns   |

| Т8   | WR to RD Pre-Charge Time           | 50  | -   | ns   |

| Т9   | Data Setup Time before WR Inactive | 20  | -   | ns   |

| T10  | Data Hold Time from WR Inactive    | 0   | -   | ns   |

| T11  | WR Inactive to TXE#                | 5   | 25  | ns   |

| T12  | TXE Inactive After WR Cycle        | 80  | -   | ns   |

#### Page 9

#### Table 8 - Data and Control Bus Signal Mode Options - SPI Interface

| Pin No. | Name | Туре   | Description                     |

|---------|------|--------|---------------------------------|

| 31      | SCLK | Input  | SPI Clock input, 12MHz maximum. |

| 32      | SDI  | Input  | SPI Serial Data Input           |

| 33      | SDO  | Output | SPI Serial Data Output          |

| 34      | CS   | Input  | SPI Chip Select Input           |

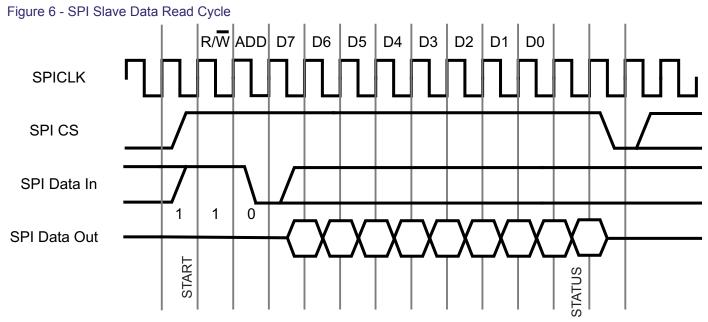

From Start - SPI CS must be held high for the entire read cycle, and must be taken low for at least one clock period after the read is completed. The first bit on SPI Data In is the R/W bit - inputting a '1' here allows data to be read from the chip. The next bit is the address bit, ADD, which is used to indicate whether the data register ('0') or the status register ('1') is read from. During the SPI read cycle a byte of data will start being output on SPI Data Out on the next clock cycle after the address bit, MSB first. After the data has been clocked out of the chip, the status of SPI Data Out should be checked to see if the data read is new data. A '0' level here on SPI Data Out means that the data read is new data. A '1' indicates that the data read is old data, and the read cycle should be repeated to get new data. Remember that CS must be held low for at least one clock period before being taken high again to continue with the next read or write cycle.

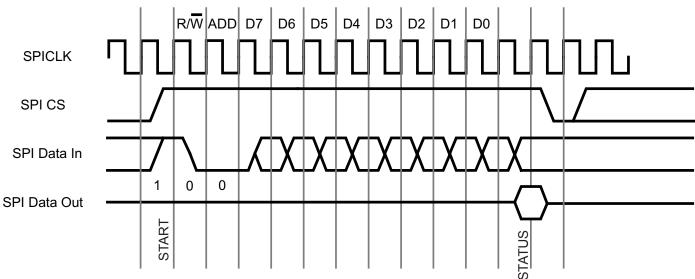

From Start - SPI CS must be held high for the entire write cycle, and must be taken low for at least one clock period after the write is completed. The first bit on SPI Data In is the R/W bit - inputting a '0' here allows data to be written to the chip. The next bit is the address bit, ADD, which is used to indicate whether the data register ('0') or the status

register ('1') is written to. During the SPI write cycle a byte of data can be input to SPI Data In on the next clock cycle after the address bit, MSB first. After the data has been clocked in to the chip, the status of SPI Data Out should be checked to see if the data read was accepted. A '0' level on SPI Data Out means that the data write was accepted. A '1' indicates that the internal buffer is full, and the write should be repeated. Remember that CS must be held low for at least one clock period before being taken high again to continue with the next read or write cycle.

Page 10

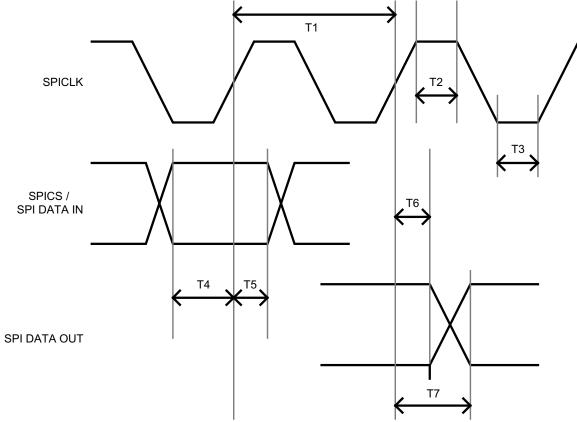

#### Figure 8 - SPI Slave Data Timing Diagrams

#### Table 9 - SPI Slave Data Timing

| Time | Description       | Min | Typical | Max | Unit |

|------|-------------------|-----|---------|-----|------|

| T1   | SPICLK Period     | 83  | -       | -   | ns   |

| T2   | SPICLK High       | 20  | -       | -   | ns   |

| Т3   | SPICLK Low        | 20  | -       | -   | ns   |

| T4   | Input Setup Time  | 10  | -       | -   | ns   |

| T5   | Input Hold Time   | 10  | -       | -   | ns   |

| Т6   | Output Hold Time  | 2   | -       | -   | ns   |

| T7   | Output Valid Time | -   | -       | 20  | ns   |

#### Table 10 - Status Register (ADD = '1')

| Bit | Description |

|-----|-------------|

| 0   | RXF#        |

| 1   | TXE#        |

| 2   | -           |

| 3   | -           |

| 4   | RXF IRQEn   |

| 5   | TXE IRQEn   |

| 6   | -           |

| 7   | -           |

#### 2.6 PS/2 Keyboard and Mouse Interface

#### Description Pin No. Name Туре 20 PS2Clk1 I/O PS/2 Keyboard or Mouse interface 1 clock signal 21 I/O PS2Data1 PS/2 Keyboard or Mouse interface 1 data signal 22 PS2Clk2 I/O PS/2 Keyboard or Mouse interface 2 clock signal 23 PS2Data2 I/O PS/2 Keyboard or Mouse interface 2 data signal

#### Table 11 - Data and Control Bus Signal Mode Options - PS/2 Keyboard and Mouse Interface

3. Package Parameters

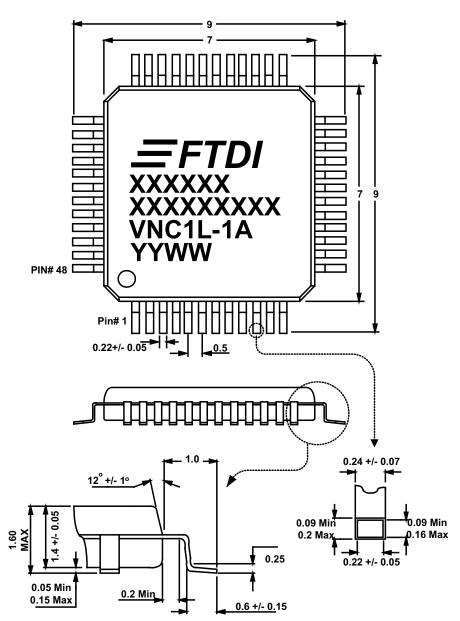

#### 3.1 LQFP-48 Dimensions

The VNC1L is supplied in a 48 pin LQFP package as standard.

Figure 9 - LQFP-48 Package Dimensions

The VNC1L is supplied in a RoHS compliant 48 pin LQFP package. The package is lead ( Pb ) free and uses a 'green' compound. The package is fully compliant with European Union directive 2002/95/EC.

This package has a 7.00mm x 7.00 mm body (9.00 mm x 9.00 mm including pins). The pins are on a 0.50 mm pitch. The above mechanical drawing shows the LQFP-48 package – all dimensions are in millimetres.

The date code format is **YYWW** where WW = 2 digit week number, YY = 2 digit year number.

An alternative 6mm x 6mm leadless QFN package is also available for projects where PCB area is critical. Contact FTDI for availability.

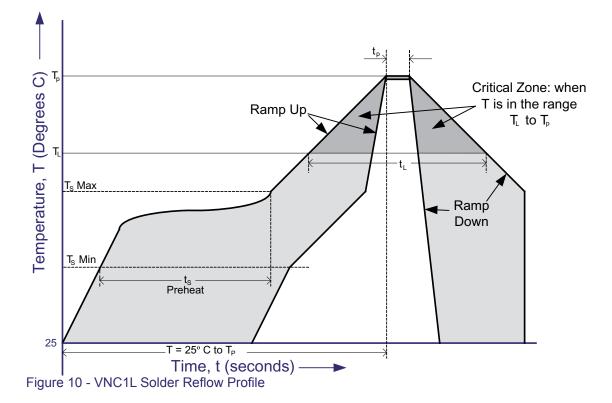

The VNC1L is supplied in Pb free 48 LD LQFP package. The recommended solder reflow profile is shown in below.

The recommended values for the solder reflow profile are detailed in Table 4. Values are shown for both a completely Pb free solder process (i.e. the VNC1L is used with Pb free solder), and for a non-Pb free solder process (i.e. the VNC1L is used with non-Pb free solder).

| Tabla | 10   | Doflow | Drofilo | Parameter |        |

|-------|------|--------|---------|-----------|--------|

| Table | 12 - | Reliow | Prome   | Parameter | values |

| Profile Feature                                                                                                                                    | Pb Free Solder Process              | Non-Pb Free Solder Process          |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------|

| Average Ramp Up Rate $(T_s \text{ to } T_p)$                                                                                                       | 3°C / second Max.                   | 3°C / Second Max.                   |

| Preheat<br>- Temperature Min (T <sub>s</sub> Min.)<br>- Temperature Max (T <sub>s</sub> Max.)<br>- Time (t <sub>s</sub> Min to t <sub>s</sub> Max) | 150°C<br>200°C<br>60 to 180 seconds | 100°C<br>150°C<br>60 to 120 seconds |

| <b>Time Maintained Above Critical Temperature T</b> <sub>L</sub> :<br>- Temperature (T <sub>L</sub> )<br>- Time (t <sub>L</sub> )                  | 217°C<br>60 to 150 seconds          | 183°C<br>60 to 150 seconds          |

| Peak Temperature (T <sub>P</sub> )                                                                                                                 | 260°C                               | 240°C                               |

| Time within 5°C of actual Peak Temperature ( $t_{\rm p}$ )                                                                                         | 20 to 40 seconds                    | 10 to 30 seconds                    |

| Ramp Down Rate                                                                                                                                     | 6°C / second Max.                   | 6°C / second Max.                   |

| Time for T= 25°C to Peak Temperature, $T_p$                                                                                                        | 8 minutes Max.                      | 6 minutes Max.                      |

#### 4.1 Absolute Maximum Ratings

The absolute maximum ratings for the VNC1L devices are as follows. These are in accordance with the Absolute Maximum Rating System (IEC 60134). Exceeding these may cause permanent damage to the device.

#### Table 13 - Absolute Maximum Ratings

| Parameter                                                                     | Value                                                         | Unit       |

|-------------------------------------------------------------------------------|---------------------------------------------------------------|------------|

| Storage Temperature                                                           | -65°C to 150°C                                                | Degrees C  |

| Floor Life (Out of Bag) At Factory Ambient<br>( 30°C / 60% Relative Humidity) | 168 Hours<br>(IPC/JEDEC J-STD-033A MSL<br>Level 3 Compliant)* | Hours      |

| Ambient Temperature (Power Applied)                                           | 0°C to 70°C                                                   | Degrees C. |

| Vcc Supply Voltage                                                            | 0 to 3.6                                                      | V          |

| D.C. Input Voltage - USBDP and USBDM                                          | 0.5 to +(Vcc +0.5)                                            | V          |

| D.C. Input Voltage - High Impedance Bidirectionals                            | -0.5 to +5.00                                                 | V          |

| D.C. Input Voltage - All other Inputs                                         | -0.5 to +(Vcc +0.5)                                           | V          |

| D.C. Output Current - Outputs                                                 | 8                                                             | mA         |

| DC Output Current - Low Impedance Bidirectionals                              | 8                                                             | mA         |

| Power Dissipation (Vcc = 3.6V)                                                | 250                                                           | mW         |

\* If devices are stored out of the packaging beyond this time limit the devices should be baked before use. The devices should be ramped up to a temperature of 125°C and baked for up to 17 hours.

#### 4.2 DC Characteristics

DC Characteristics ( Ambient Temperature = 0°C to +70°C )

#### Table 14 - Operating Voltage and Current

| Parameter | Description                    | Min | Тур | Max | Units | Conditions       |

|-----------|--------------------------------|-----|-----|-----|-------|------------------|

| Vcc1      | VCC Operating Supply Voltage   | 3.0 | 3.3 | 3.6 | V     |                  |

| Vcc2      | VCCIO Operating Supply Voltage | 3.0 | 3.3 | 3.6 | V     |                  |

| lcc1      | Operating Supply Current       | -   | 25  | -   | mA    | Normal Operation |

| lcc2      | Operating Supply Current       | 1   | -   | 2   | ΜA    | USB Suspend      |

#### Table 15 - UART and CBUS I/O Pin Characteristics

| Parameter | Description               | Min     | Тур | Max | Units | Conditions     |

|-----------|---------------------------|---------|-----|-----|-------|----------------|

| Voh       | Output Voltage High       | Vcc-0.4 |     |     | V     | I source = 8mA |

| Vol       | Output Voltage Low        |         |     | 0.4 | V     | l sink = 8mA   |

| Vin       | Input Switching Threshold | 0.8     | 1.4 | 2.0 | V     | **             |

#### Table 16 - RESET# and PROG# Pin Characteristics

| Parameter | Description               | Min | Тур | Max | Units | Conditions |

|-----------|---------------------------|-----|-----|-----|-------|------------|

| Vin       | Input Switching Threshold | 0.8 | 1.4 | 2.0 | V     |            |

#### Table 17 - USB I/O Pin (USBDP, USBDM) Characteristics

| Parameter | Description                    | Min | Тур | Max | Units | Conditions |

|-----------|--------------------------------|-----|-----|-----|-------|------------|

| UVoh      | I/O Pins Static Output (High)  | 2.8 |     | 3.6 | V     |            |

| UVol      | I/O Pins Static Output ( Low ) | 0   |     | 0.3 | V     |            |

| UVse      | Single Ended Rx Threshold      | 0.8 |     | 2.0 | V     |            |

| UCom      | Differential Common Mode       | 0.8 |     | 2.5 | V     |            |

| UVDif     | Differential Input Sensitivity | 0.2 |     |     | V     |            |

| UDrvZ     | Driver Output Impedance        | 28  |     | 44  | Ohms  | ***        |

\*\*\*Driver Output Impedance includes the external USB series resistors on USBDP and USBDM pins.

#### Table 18 - XTIN, XTOUT Pin Characteristics

| Parameter | Description               | Min | Тур | Max | Units | Conditions   |

|-----------|---------------------------|-----|-----|-----|-------|--------------|

| Voh       | Output Voltage High       |     | 0.6 |     | V     | Fosc = 12MHz |

| Vol       | Output Voltage Low        |     | 0.2 |     | V     | Fosc = 12MHz |

| Vin       | Input Switching Threshold |     | 0.4 |     | V     |              |

## 5. Device Configurations

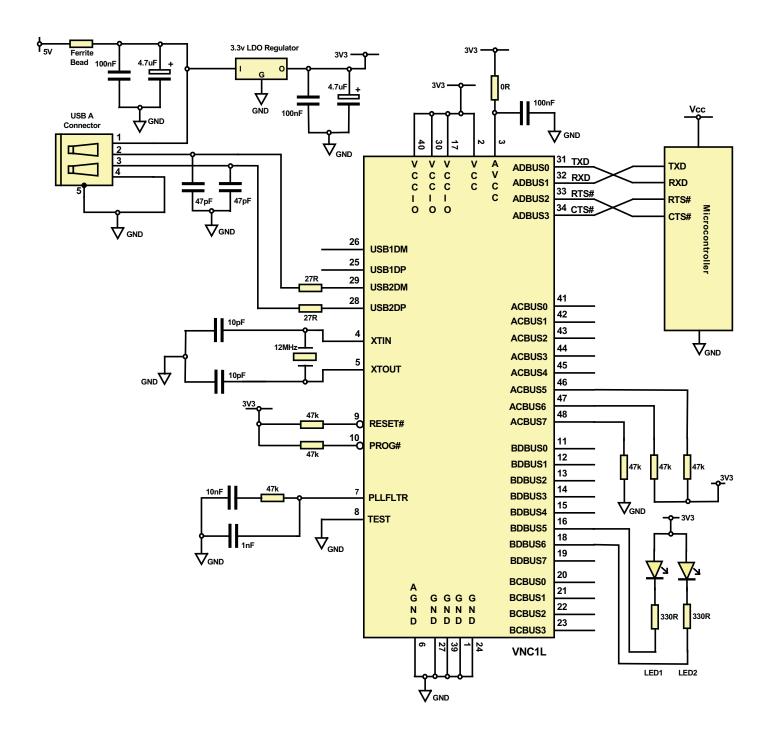

#### 5.1 Example VNC1L Schematic (MCU - UART interface)

# Copyright © Future Technology Devices International Limited , 2006.

Version 0.90 - Initial Datasheet Created July 2006 Version 0.95 - Datasheet Update September 2006 Version 0.96 - Datasheet Update March 2007 Version 0.97 - Update table 5. June 2007

Neither the whole nor any part of the information contained in, or the product described in this manual, may be adapted or reproduced in any material or electronic form without the prior written consent of the copyright holder.

This product and its documentation are supplied on an as-is basis and no warranty as to their suitability for any particular purpose is either made or implied.

Future Technology Devices International Ltd. will not accept any claim for damages howsoever arising as a result of use or failure of this product. Your statutory rights are not affected.

This product or any variant of it is not intended for use in any medical appliance, device or system in which the failure of the product might reasonably be expected to result in personal injury.

This document provides preliminary information that may be subject to change without notice.

#### **Contact FTDI**

#### Head Office -

**Future Technology Devices International Ltd.** 373 Scotland Street, Glasgow G5 8QB, United Kingdom

Tel. : +(44) 141 429 2777 Fax. : +(44) 141 429 2758

E-Mail (Sales) : vinculum.sales@ftdichip.com E-Mail (Support) : vinculum.support1@ftdichip.com

E-Mail (General Enquiries) : admin1@ftdichip.com Regional Sales Offices -

# Future Technology Devices International Ltd. (Taiwan)

4F, No 18-3, Sec. 6 Mincyuan East Road, Neihu District, Taipei 114, Taiwan, R.o.C.

Tel.: +886 2 8791 3570 Fax: +886 2 8791 3576

E-Mail (Sales): tw.sales1@ftdichip.com E-Mail (Support): tw.support@ftdichip.com

E-Mail (General Enquiries): us.admin@ftdichip.com

FTDI Company website URL : http://www.ftdichip.com Vinculum dedicated product website URL : http://www.vinculum.com

E-Mail (General Enquiries): tw.admin@ftdichip.com

# Future Technology Devices International Ltd. (USA)

7235 NW Evergreen Parkway, Suite 600 Hillsboro, OR 97124-5803 USA

Tel.: +1 (503) 547-0988 Fax: +1 (503) 547-0987

E-Mail (Sales): us.sales@ftdichip.com E-Mail (Support): us.support@ftdichip.com